DARPA Selects Rajit Manohar For Chip Innovation Program

Rajit Manohar, the John C. Malone Professor of Electrical Engineering and Computer Science, has been selected for a DARPA-funded four-year program designed to spark the next wave of semiconductor innovation and circuit design in the U.S.

The overall goal of the effort, from the Defense Advanced Research Projects Agency (DARPA), is to greatly reduce the resources, expertise and time it takes to develop new chips. Demand for System-on-Chip (SoC) platforms has remained strong but the cost to design this technology has increased to the point where smaller companies often don’t have the resources to design these circuits for specialized applications. That leaves it to a few large corporations to fill the demand - and little room for innovation.

The overall goal of the effort, from the Defense Advanced Research Projects Agency (DARPA), is to greatly reduce the resources, expertise and time it takes to develop new chips. Demand for System-on-Chip (SoC) platforms has remained strong but the cost to design this technology has increased to the point where smaller companies often don’t have the resources to design these circuits for specialized applications. That leaves it to a few large corporations to fill the demand - and little room for innovation.

Aiming to correct that, DARPA formed the Electronics Resurgence Initiative (ERI), which brings together researchers from academia, commercial industry, and the defense industrial base to address today’s SoC design complexity and cost barriers.

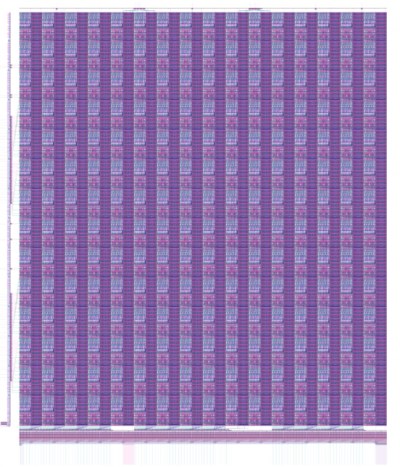

As part of the program, Manohar and his team will be working on two collaborative projects, funded for a total of about $12 million. Both aim to develop open-source software tools for electronic design automation (EDA) of asynchronous chips. Because today’s chips are so complex - they can have billions of components - automation tools are necessary for their design.

Systems with asynchronous circuits allow each function as little or as much time as needed to complete its task. This differs from systems with synchronous circuits - the industry standard - guided by built-in clocks that allow the same amount of time for the completion of each computational function. This means that the system can run only as fast as the slowest function that is supported. Because the time for each function in an asynchronous circuit can be different, the systems works more efficiently taking only as much time as necessary rather than the time taken by the slowest function.

The problem, Manohar said, is that there’s no universally available set of tools to design asynchronous chips, and it’s prohibitively costly and time-consuming for companies to make their own.

“Right now, it’s a chicken-or-the-egg problem for people trying to use these circuits,” he said. “You can’t design something complicated without tools, but third-party vendors won’t produce the tools if they don’t already have customers. The goal of this project is to create an open-source tool flow that we and other people can use to design these asynchronous chips and break this deadlock.”

Besides making the tools available to other researchers in industry and academia, Manohar said he will be using them in his classes.

Manohar will be working with Sandia National Labs, the University of Texas at Austin, and Texas State University.